AIM:

To simulate the arithmetic functions of 4-bit adder & subtractor with addition, subtraction and multiplication.

APPARATUS REQUIRED:

Xilinx V14.7 Software

1. 4-BIT ADDER:

Logic Diagrams:

Programs:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity adder is

Port (

x: in STD_LOGIC_VECTOR (3 downto 0);

y : in STD_LOGIC_VECTOR (3 downto 0);

cin : in STD_LOGIC;

sum : out STD_LOGIC_VECTOR (3 downto 0);

cout : out STD_LOGIC);

end adder;

architecture Behavioral of adder is

component fulladder

port(

x,y,cin:in std_logic;

sum,cout: out std_logic);

end component;

signal c: std_logic_vector(2 downto 0);

begin

a1:fulladder port map(x(0), y(0), cin, sum(0), c(0));

a2:fulladder port map(x(1), y(1), c(0), sum(1), c(1));

a3:fulladder port map(x(2), y(2), c(1), sum(2), c(2));

a4:fulladder port map(x(3), y(3), c(2), sum(3), cout);

end Behavioral;

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port(

x,y,cin:in std_logic;

sum,cout: out std_logic);

end fulladder;

architecture comb of fulladder is

begin

sum <= x xor y xor cin;

cout <= (x and y) or (cin and (x xor y));

end comb;

Simulation Output:

2. 4-BIT SUBTRACTOR:

Logic Diagrams:

Programs:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity subtraction is

Port (

a: in STD_LOGIC_VECTOR (3 downto 0);

b : in STD_LOGIC_VECTOR (3 downto 0);

cin : in STD_LOGIC;

diff : out STD_LOGIC_VECTOR (3 downto 0);

br : out STD_LOGIC);

end subtraction;

architecture Behavioral of subtraction is

component fullsubtraction

port(

a,b,c:in std_logic;

diff,br: out std_logic);

end component;

signal c: std_logic_vector(2 downto 0);

begin

a1:fullsubtraction port map(a(0), b(0), cin, diff(0), c(0));

a2:fullsubtraction port map(a(1), b(1), c(0), diff(1), c(1));

a3:fullsubtraction port map(a(2), b(2), c(1), diff(2), c(2));

a4:fullsubtraction port map(a(3), b(3), c(2), diff(3), br);

end Behavioral;

library ieee;

use ieee.std_logic_1164.all;

entity fullsubtraction is

port(

a,b,c:in std_logic;

diff,br: out std_logic);

end fullsubtraction;

architecture Behavioral of fullsubtraction is

begin

diff <= a xor b xor c;

br <= ((not a )and b) or ((not a )and c) or (b and c);

end Behavioral;

Simulation Output:

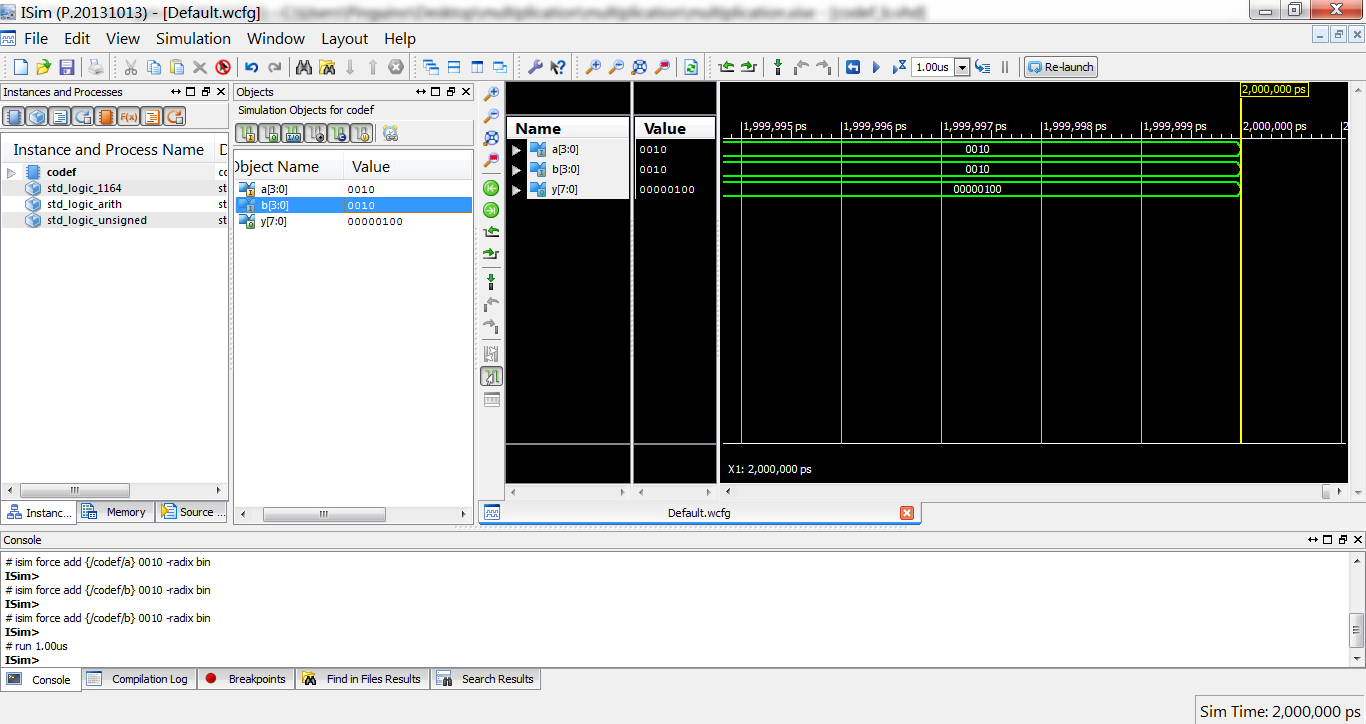

3. ADDITION, SUBTRACTION, MULTIPLICATION:

Programs:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity codef is

Port (

a : in STD_LOGIC_VECTOR (3 downto 0);

b : in STD_LOGIC_VECTOR (3 downto 0);

y : out STD_LOGIC_VECTOR (7 downto 0));

end codef;

architecture Behavioral of codef is

begin

y <= a * b;

end Behavioral;

Simulation Output:

FLOW CHART:

PROCEDURES:

Step1: Open xilinx software > go to file > new project > create source file name> select specific folder> next > select proper project settings> we use spartan 3E trainer kit.

Step2: next > finish > go to project > new source > select VHDL module > create file name> next > select input and output > next > finish> write program > if done write programs > click synthesis > right click> run.

Step3: if completed successfully > go to simulation > click source file > right click > new source > select VHDL test bench > create simulation file name > next > select source file > next > finish.

Step4: select simulation file > Isim simulator > click behavioral check syntax > right click > run > if successfully completed. click simulation behavioral > right click > run > wait few seconds > will open new tap.

Step5: click object name > right click > select force constant >

Step6: set all input value > click Run for the time specified on the toolbar> check simulation output in this screen

NOTE: if you want image file > click print screen > open MS paint > cnt +v > save

if you want PDF file > file > print > select doPDF printer > create pdf file name + quality> ok

To simulate the arithmetic functions of 4-bit adder & subtractor with addition, subtraction and multiplication.

APPARATUS REQUIRED:

Xilinx V14.7 Software

1. 4-BIT ADDER:

Logic Diagrams:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity adder is

Port (

x: in STD_LOGIC_VECTOR (3 downto 0);

y : in STD_LOGIC_VECTOR (3 downto 0);

cin : in STD_LOGIC;

sum : out STD_LOGIC_VECTOR (3 downto 0);

cout : out STD_LOGIC);

end adder;

architecture Behavioral of adder is

component fulladder

port(

x,y,cin:in std_logic;

sum,cout: out std_logic);

end component;

signal c: std_logic_vector(2 downto 0);

begin

a1:fulladder port map(x(0), y(0), cin, sum(0), c(0));

a2:fulladder port map(x(1), y(1), c(0), sum(1), c(1));

a3:fulladder port map(x(2), y(2), c(1), sum(2), c(2));

a4:fulladder port map(x(3), y(3), c(2), sum(3), cout);

end Behavioral;

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port(

x,y,cin:in std_logic;

sum,cout: out std_logic);

end fulladder;

architecture comb of fulladder is

begin

sum <= x xor y xor cin;

cout <= (x and y) or (cin and (x xor y));

end comb;

Simulation Output:

2. 4-BIT SUBTRACTOR:

Logic Diagrams:

Programs:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity subtraction is

Port (

a: in STD_LOGIC_VECTOR (3 downto 0);

b : in STD_LOGIC_VECTOR (3 downto 0);

cin : in STD_LOGIC;

diff : out STD_LOGIC_VECTOR (3 downto 0);

br : out STD_LOGIC);

end subtraction;

architecture Behavioral of subtraction is

component fullsubtraction

port(

a,b,c:in std_logic;

diff,br: out std_logic);

end component;

signal c: std_logic_vector(2 downto 0);

begin

a1:fullsubtraction port map(a(0), b(0), cin, diff(0), c(0));

a2:fullsubtraction port map(a(1), b(1), c(0), diff(1), c(1));

a3:fullsubtraction port map(a(2), b(2), c(1), diff(2), c(2));

a4:fullsubtraction port map(a(3), b(3), c(2), diff(3), br);

end Behavioral;

library ieee;

use ieee.std_logic_1164.all;

entity fullsubtraction is

port(

a,b,c:in std_logic;

diff,br: out std_logic);

end fullsubtraction;

architecture Behavioral of fullsubtraction is

begin

diff <= a xor b xor c;

br <= ((not a )and b) or ((not a )and c) or (b and c);

end Behavioral;

Simulation Output:

3. ADDITION, SUBTRACTION, MULTIPLICATION:

Programs:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity codef is

Port (

a : in STD_LOGIC_VECTOR (3 downto 0);

b : in STD_LOGIC_VECTOR (3 downto 0);

y : out STD_LOGIC_VECTOR (7 downto 0));

end codef;

architecture Behavioral of codef is

begin

y <= a * b;

end Behavioral;

Simulation Output:

FLOW CHART:

PROCEDURES:

Step1: Open xilinx software > go to file > new project > create source file name> select specific folder> next > select proper project settings> we use spartan 3E trainer kit.

Step2: next > finish > go to project > new source > select VHDL module > create file name> next > select input and output > next > finish> write program > if done write programs > click synthesis > right click> run.

Step3: if completed successfully > go to simulation > click source file > right click > new source > select VHDL test bench > create simulation file name > next > select source file > next > finish.

Step4: select simulation file > Isim simulator > click behavioral check syntax > right click > run > if successfully completed. click simulation behavioral > right click > run > wait few seconds > will open new tap.

Step5: click object name > right click > select force constant >

Step6: set all input value > click Run for the time specified on the toolbar> check simulation output in this screen

NOTE: if you want image file > click print screen > open MS paint > cnt +v > save

if you want PDF file > file > print > select doPDF printer > create pdf file name + quality> ok

No comments:

Post a Comment